تصميم وتنفيذ دوائر رقمية باستخدام Verilog و FPGA

تصميم وتنفيذ دوائر رقمية باستخدام Verilog و FPGA

وصف الخدمة

وصف الخدمة

أقدّم خدمة تصميم وتنفيذ الدوائر الرقمية باستخدام Verilog و FPGA مع إجراء المحاكاة (Simulation) والتحقق من صحة التصميم (Verification) قبل التسليم.

تشمل الخدمة:

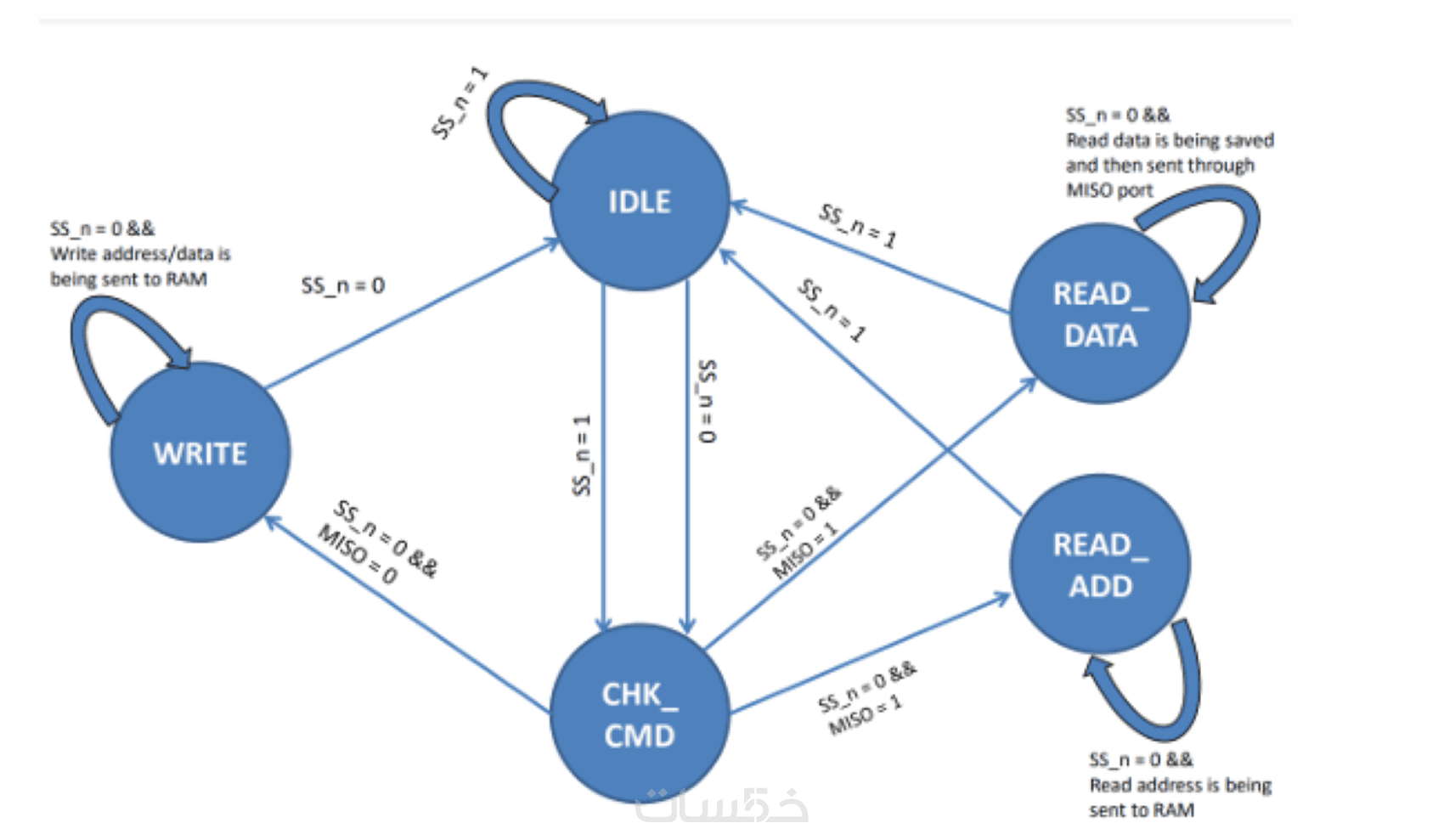

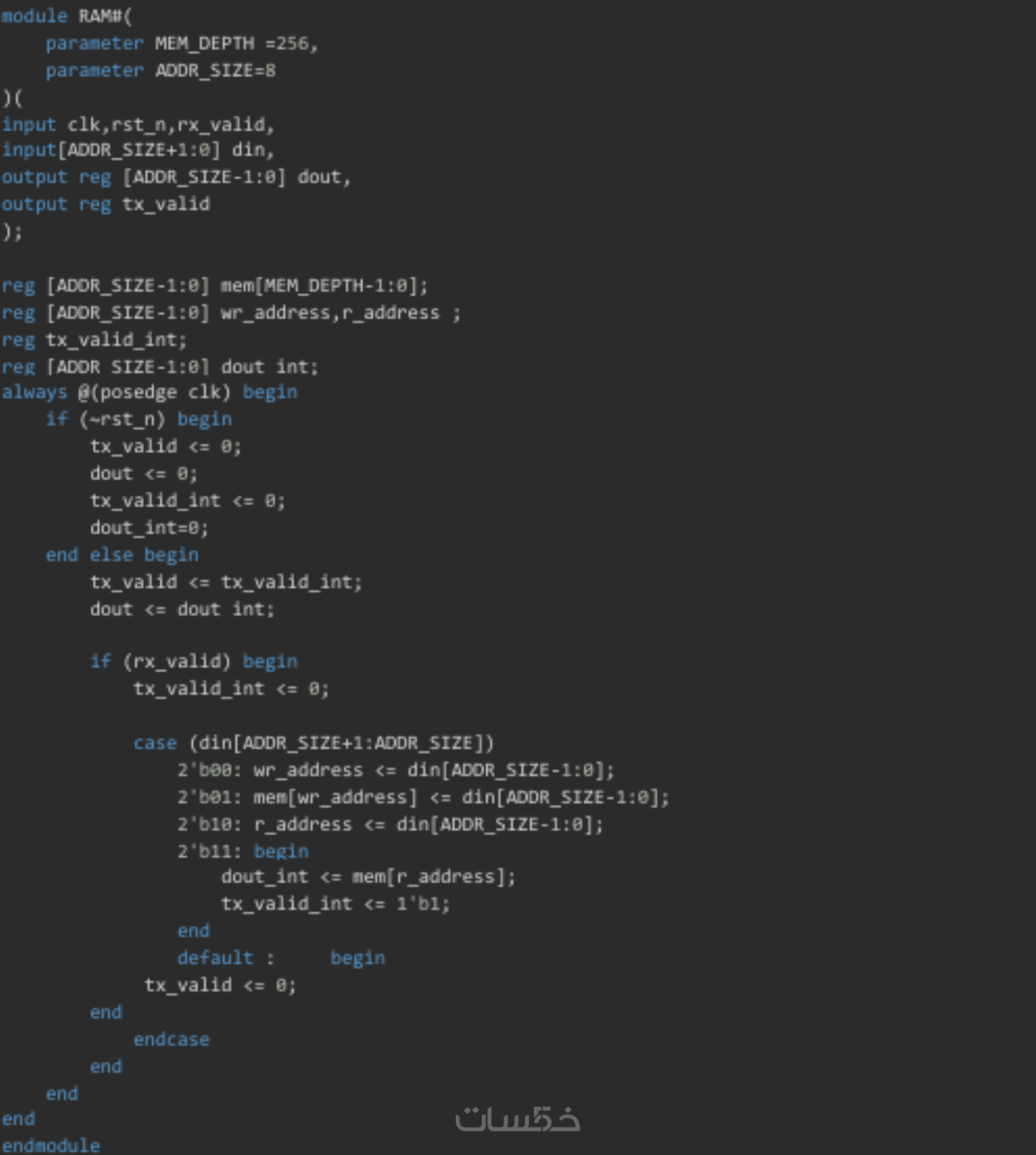

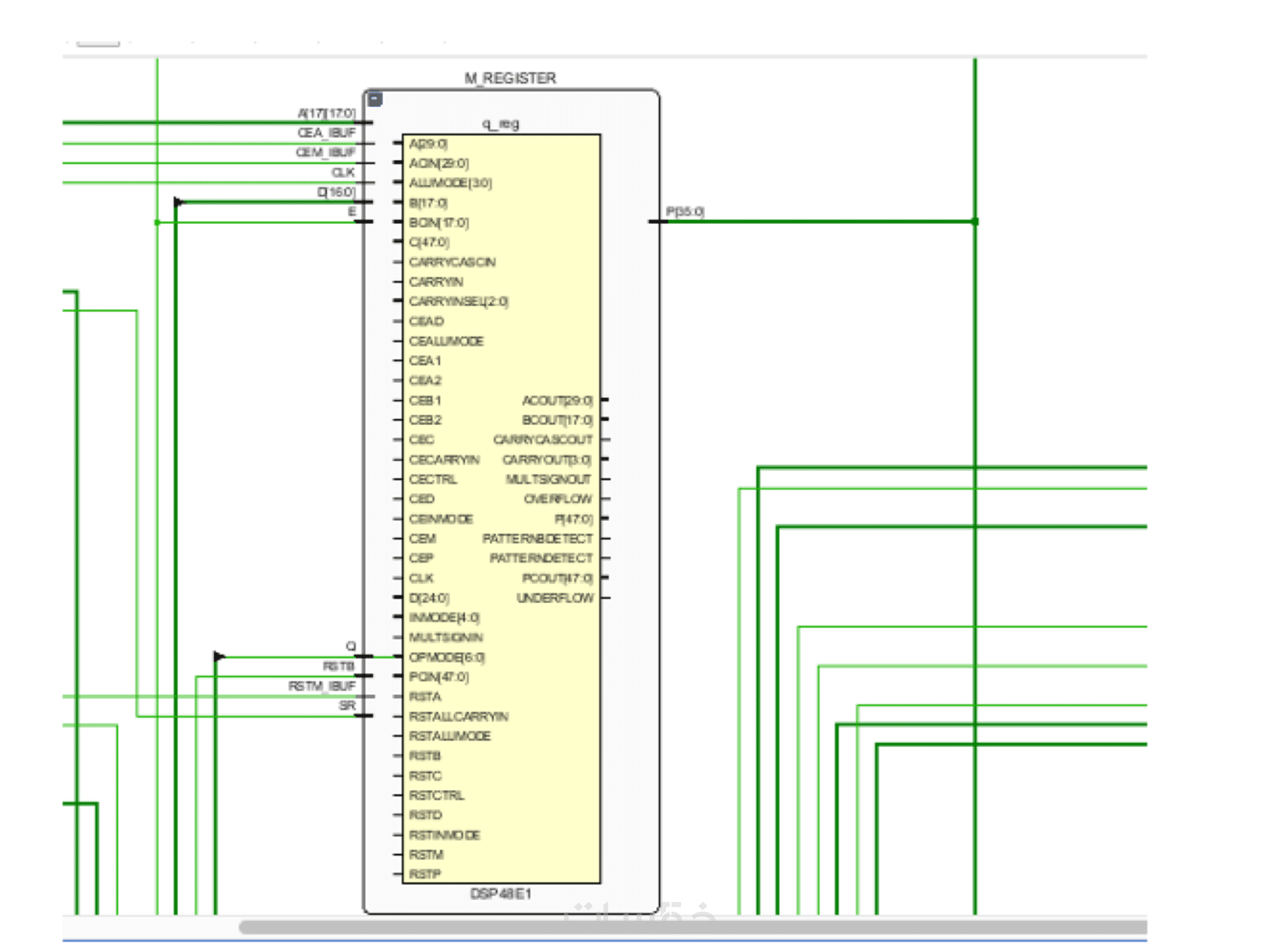

- تصميم وحدات رقمية مثل: ALU، FIFO، SPI، RAM، Counters، FSM

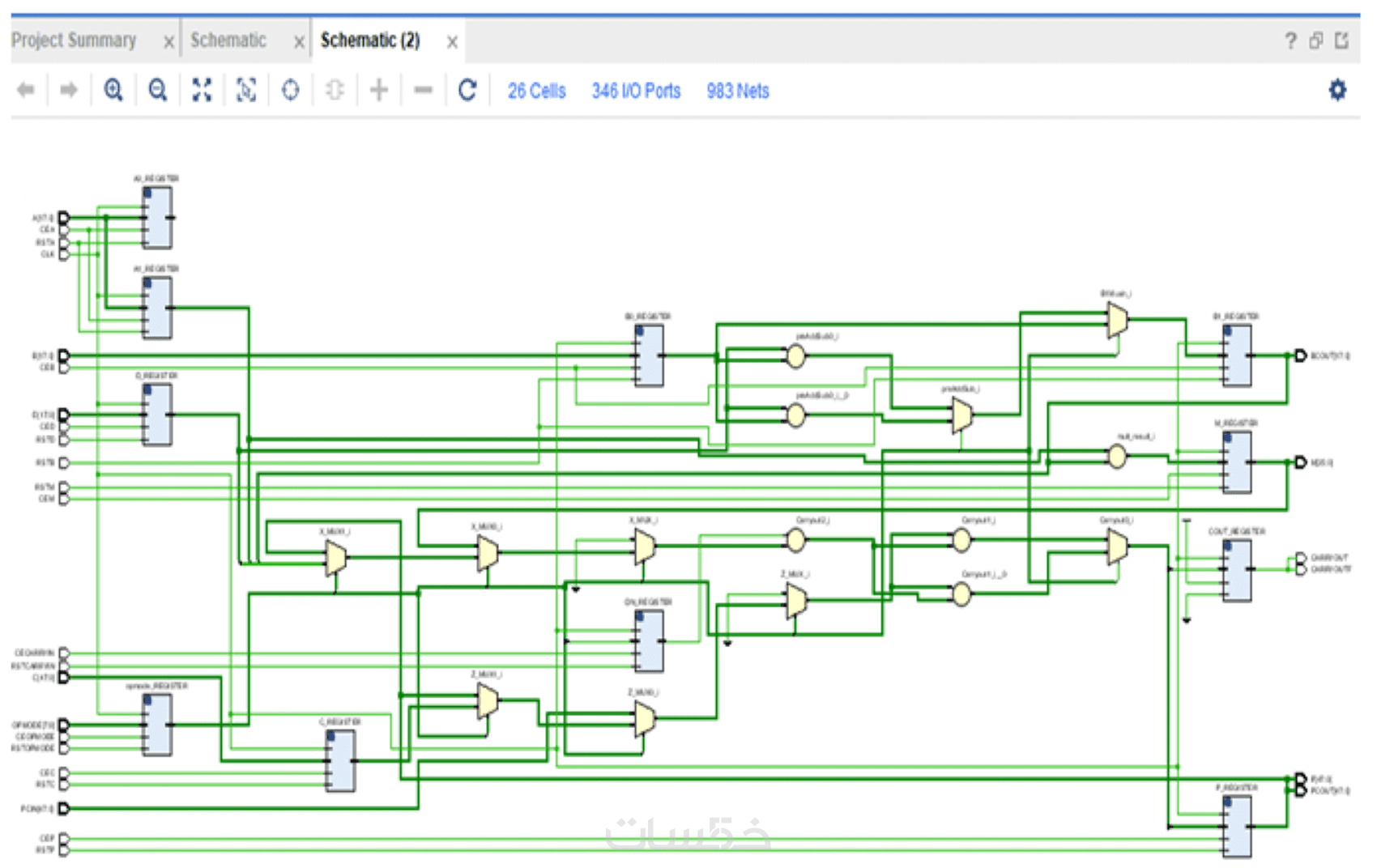

- كتابة كود Verilog منظم وقابل للتطوير (Modular Design)

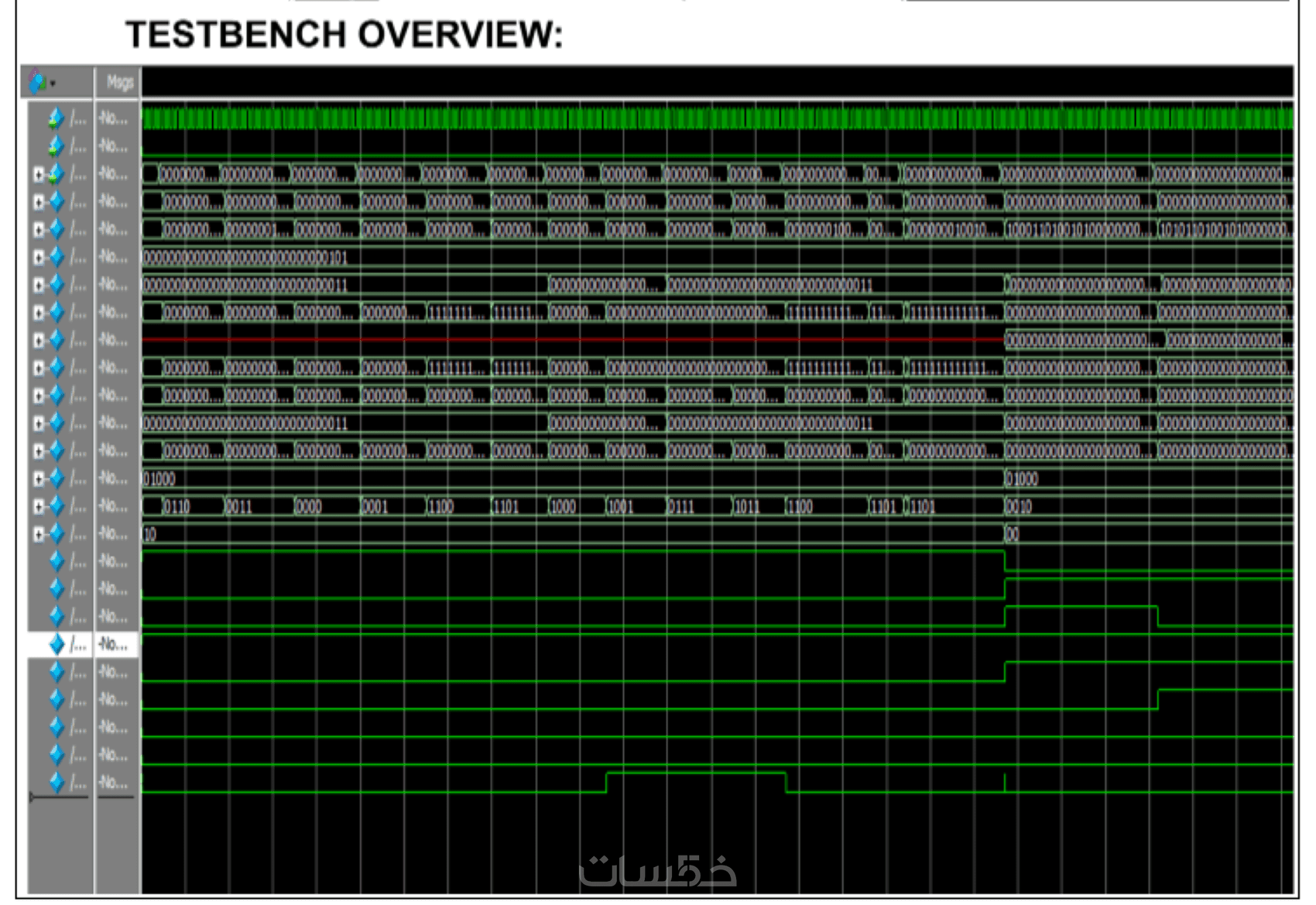

- إنشاء Testbench لإجراء المحاكاة والتحقق من النتائج

- مراجعة وتصحيح وتحسين أكواد Verilog الموجودة

التسليم يتضمن:

- كود Verilog منظم ومشروح

-Testbench كامل

- نتائج المحاكاة (Waveforms أو Screenshots)

- شرح مبسط لآلية عمل التصميم

تفاصيل الباقة الأساسية:

-تصميم وحدة رقمية واحدة (Module) حتى 200 سطر كود

-عدد 1 Testbench

-عدد 2 تعديل (Revision)

تطويرات إضافية متاحة:

- تصميم أكثر من Module

- زيادة عدد الأسطر أو التعقيد المنطقي

- إضافة بروتوكولات أو Interfaces متقدمة

يتم تحديد السعر النهائي بناءً على:

- عدد الوحدات المطلوبة

- عدد الأسطر التقريبي

- نوع الوظيفة المطلوبة (Arithmetic / Control / Communication)

مميزات الخدمة

كود منظم واحترافي

تصميم RTL منظم، واضح، وقابل لإعادة الاستخدام، مع الالتزام بأفضل ممارسات Digital Design.

محاكاة وتحقيق كامل

تشغيل Simulation باستخدام ModelSim أو QuestaSim للتحقق من صحة جميع الحالات الوظيفية.

Verification احترافي للتصميم

التحقق الوظيفي الكامل للتصميم من خلال كتابة Testbench باستخدام UVMو Verilog و SystemVerilog، واختبار جميع الحالات المتوقعة لضمان عمل الدائرة بشكل صحيح قبل التسليم.

مشاريع Arduino و Embedded Systems

تنفيذ مشاريع Arduino باستخدام لغة C، والتعامل مع الحساسات، الشاشات، وبروتوكولات الاتصال مثل UART

تسليم في الوقت المحدد

الالتزام بموعد التسليم والتواصل المستمر مع العميل حتى اكتمال العمل بالشكل المطلوب.